基于FPGA的AD7606數(shù)據(jù)采集與UDP網(wǎng)絡(luò)傳輸系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

本文詳細(xì)介紹一種基于FPGA的AD7606數(shù)據(jù)采集系統(tǒng),通過UDP協(xié)議實(shí)現(xiàn)網(wǎng)絡(luò)傳輸,并提供完整的工程源碼、技術(shù)支持及上位機(jī)接收軟件。該系統(tǒng)在工業(yè)自動化、測試測量等領(lǐng)域具有廣泛應(yīng)用價(jià)值。

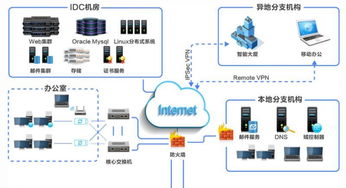

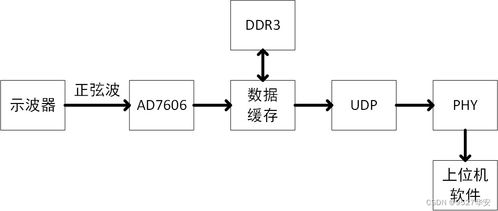

一、系統(tǒng)架構(gòu)設(shè)計(jì)

本系統(tǒng)采用模塊化設(shè)計(jì)思想,主要包含以下核心模塊:

- AD7606采集控制模塊:FPGA通過SPI接口控制AD7606模數(shù)轉(zhuǎn)換器,實(shí)現(xiàn)8通道16位同步數(shù)據(jù)采集,最高采樣率可達(dá)200KSPS

- 數(shù)據(jù)緩存與處理模塊:采用雙緩沖機(jī)制,確保數(shù)據(jù)連續(xù)采集不丟失,同時(shí)支持?jǐn)?shù)字濾波和數(shù)據(jù)校準(zhǔn)功能

- UDP網(wǎng)絡(luò)傳輸模塊:集成MAC和PHY控制器,實(shí)現(xiàn)千兆以太網(wǎng)通信,通過UDP協(xié)議將采集數(shù)據(jù)打包發(fā)送

二、關(guān)鍵技術(shù)實(shí)現(xiàn)

- AD7606接口設(shè)計(jì)

- 配置FPGA的GPIO模擬SPI時(shí)序

- 設(shè)計(jì)采樣時(shí)鐘產(chǎn)生邏輯

- 實(shí)現(xiàn)數(shù)據(jù)讀取和校驗(yàn)機(jī)制

- UDP傳輸優(yōu)化

- 采用固定長度數(shù)據(jù)包(1472字節(jié)載荷)

- 實(shí)現(xiàn)硬件CRC校驗(yàn)

- 集成ARP、ICMP協(xié)議支持

- 時(shí)序同步機(jī)制

- 采用PLL產(chǎn)生精確時(shí)鐘

- 實(shí)現(xiàn)采集與傳輸時(shí)鐘域隔離

- 設(shè)計(jì)時(shí)間戳插入功能

三、工程源碼特點(diǎn)

提供的Verilog/VHDL源碼包含:

- 完整的Quartus/Vivado工程文件

- 約束文件和引腳分配

- 仿真測試平臺

- 詳細(xì)的注釋文檔

四、上位機(jī)接收軟件

基于C#開發(fā)的上位機(jī)軟件具備:

- 實(shí)時(shí)數(shù)據(jù)顯示和波形繪制

- 數(shù)據(jù)存儲和回放功能

- 網(wǎng)絡(luò)參數(shù)配置界面

- 數(shù)據(jù)導(dǎo)出和報(bào)表生成

五、系統(tǒng)性能指標(biāo)

- 采樣精度:16位

- 傳輸延遲:<1ms

- 數(shù)據(jù)吞吐量:≥80Mbps

- 網(wǎng)絡(luò)協(xié)議:UDP/IPv4

六、應(yīng)用場景

本系統(tǒng)適用于:

- 工業(yè)現(xiàn)場數(shù)據(jù)采集

- 實(shí)驗(yàn)室測試測量

- 嵌入式系統(tǒng)開發(fā)

- 物聯(lián)網(wǎng)數(shù)據(jù)終端

七、技術(shù)支持服務(wù)

提供包括:

- 硬件設(shè)計(jì)指導(dǎo)

- 軟件調(diào)試支持

- 定制化開發(fā)服務(wù)

- 技術(shù)文檔更新

本解決方案經(jīng)過實(shí)際驗(yàn)證,具有可靠性高、實(shí)時(shí)性好、擴(kuò)展性強(qiáng)等特點(diǎn),為相關(guān)領(lǐng)域工程師提供了完整的技術(shù)參考和實(shí)現(xiàn)方案。

如若轉(zhuǎn)載,請注明出處:http://www.xsge.com.cn/product/32.html

更新時(shí)間:2026-01-08 09:16:37